產品中心

本文深入探討了開關電源中傳導電磁干擾(EMI)問題的成因及其對系統性能的影響。通過合理的優化設計方法,如使用差模和共模濾波器、優化PCB布局等手段來有效減少干擾,幫助工程師們構建更高效、更可靠的電源解決方案。

電磁干擾(EMI)在各個應用領域中都干擾著系統的穩定性和信號的完好性,既然無法避免,那如何更多地從設計的角度解決問題是關鍵,下面我們來分析開關電源中常見的幾種EMI問題。

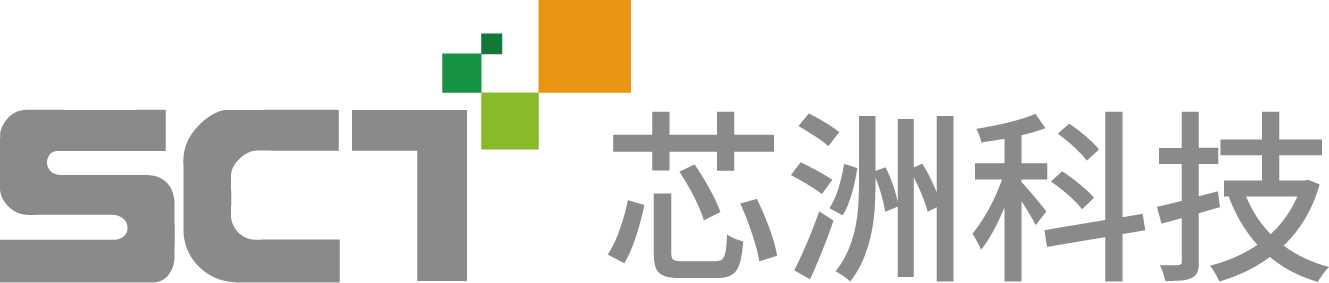

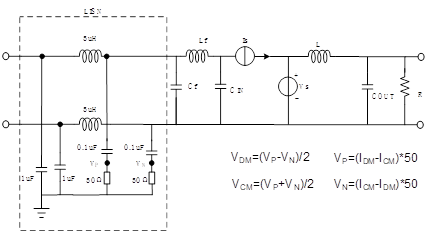

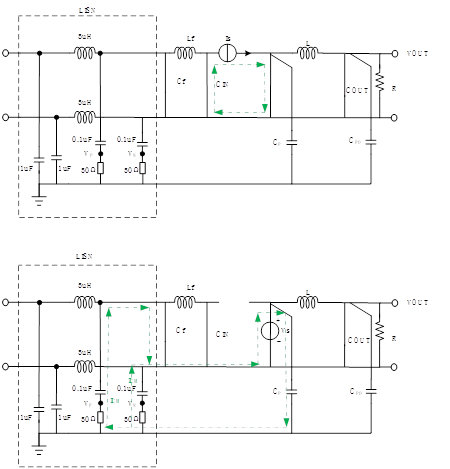

如圖所示在傳導發射測試中干擾信號由LISN感應,由此我們可以根據LISN進行差模(DM)和共模(CM)干擾模型的建立。以BUCK電路為例。

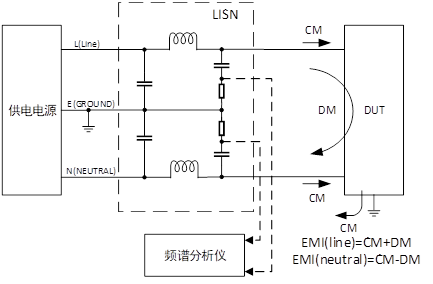

對于圖2使用電流源替代開關管,使用電壓源替代SW電壓。其中IS波形與HIS 相同,VS波形與VSW相同。

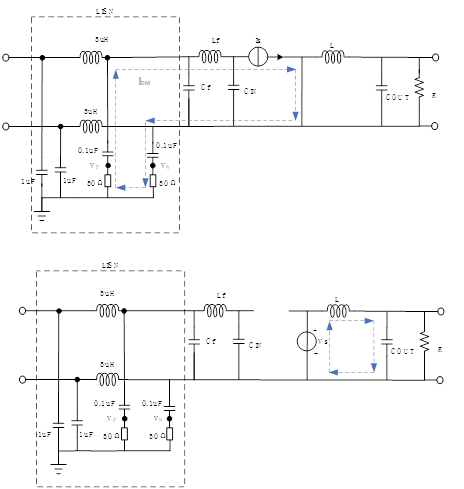

使用疊加原理進行化簡,分別將電壓源短路和電流源斷路。

圖4 疊加原理分解后差模等效電路

由圖4可知差模干擾能被LISN感知的主要集中在IS通路中同時在高頻交流干擾,0.1uF可以等效為短路,則BUCK電路差模模型可簡化為下圖。

由此可知差模干擾主要由IS引起。IS 與開關管電流波形相同。差模干擾主要由輸入回路中電流變化(di/dt)所產生。

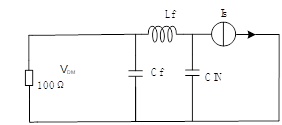

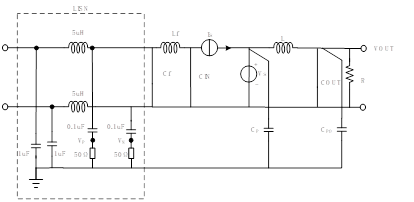

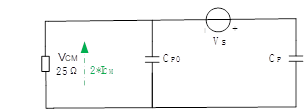

同理進行共模模型的簡化,共模干擾主要由寄生電容和機殼、銅皮組成的回路進行傳遞。所以引入SW到大地的寄生電容CP,輸出到大地寄生電容CPO。同時共模干擾為輸入線徑中相同分量,所以將Cf和CIN等效為短路,最終如下圖所示。

同樣進行疊加原理

繼續簡化可得下圖

由此可知共模干擾主要由VS引起,VS 與SW波形相同,則共模干擾主要由SW處電壓變化(dv/dt)所產生。